Статья опубликована в рамках: XXVIII Международной научно-практической конференции «Научное сообщество студентов XXI столетия. ТЕХНИЧЕСКИЕ НАУКИ» (Россия, г. Новосибирск, 29 января 2015 г.)

Наука: Технические науки

Секция: Радиотехника, Электроника

Скачать книгу(-и): Сборник статей конференции

- Условия публикаций

- Все статьи конференции

дипломов

МАРШРУТ РАЗРАБОТКИ ЦИФРОВОЙ СБИС НА ОСНОВЕ БМК

Нидеккер Леонид Георгиевич

магистрант 1 курса, кафедра микро- и наноэлектроники, факультет физической и квантовой электроники, МФТИ, РФ, г. Зеленоград

E -mail: nidekker@phystech.edu

Эннс Виктор Иванович

научный руководитель, канд. техн. наук, кафедра микро- и наноэлектроники, МФТИ, РФ, г. Зеленоград.

Введение

В настоящее время производство интегральных микросхем можно разделить на изготовление заказных и полузаказных СБИС. В свою очередь полузаказные СБИС делятся на два конкурирующих типа, а именно, микросхемы на основе базовых матричных кристаллов (БМК) и программируемые логические интегральные схемы (ПЛИС). Каждый из представленных типов имеет свои характерные преимущества и недостатки. Так, например, производство интегральных микросхем на основе БМК удобно при следующих обстоятельствах:

· Когда необходимо в кротчайшие сроки разработать и начать производство изделия (так как разработка микросхемы на основе БМК в 3—5 раз быстрее и дешевле, по сравнению с разработкой полностью заказной СБИС);

· Когда объем производства не слишком высок (при серийности от 1 до 40—50 тысяч);

· При желании заказчика самостоятельно разработать БМК с целью, например, скрыть свое “know-how”.

С другой стороны, к недостаткам использования БМК можно отнести неоптимальность полученного результата, а именно проигрыш по площади и быстродействию микросхемы (по сравнению с полностью заказными СБИС), так как часть элементов БМК оказывается избыточной, взаимное расположение элементов и пути межсоединений не являются наилучшими и т. д. [1]

Интегральные микросхемы на основе базовых матричных кристаллов нашли применение в различных отраслях производства, например при изготовлении аппаратуры специального назначения, в космической промышленности и др.

Общий вид маршрута проектирования цифровой СБИС на БМК

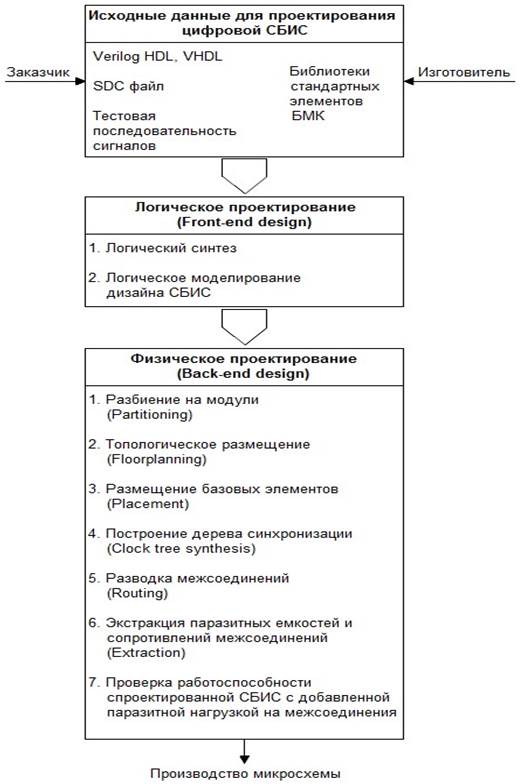

Стандартный маршрут проектирования интегральной микросхемы на основе БМК представлен на рис. 1. Следует отметить, что, так как подходы к проектированию цифровых и аналоговых схем несколько отличаются, то дальнейшие рассуждения будут относиться исключительно к цифровым схемам.

Итак, в общем случае процесс разработки СБИС состоит из двух частей, а именно из логического проектирования (front-end design) и физического проектирования (back-end design). На первый взгляд может показаться, что эти два этапа проектирования обособленны друг от друга и взаимодействуют только посредством входных или выходных данных (имеется в виду, что результаты логического проектирования берутся как входные данные для физического проектирования), однако на практике это не так. В ряде случаев, во время физического проектирования необходимо возвращаться к этапу логического синтеза для достижения наилучшего результата.

Исходные данные для проектирования можно условно разделить на две группы. К первой группе относится информация, предоставляемая заказчиком. Основным элементом данной группы является формальное описание проекта, на каком-либо языке моделирования аппаратных средств (как правило, используют либо VHDL, либо Verilog HDL).

Рисунок 1. Маршрут проектирования цифровой СБИС на основе БМК

Однако на практике возможны и другие ситуации, например: описание устройства предоставляется заказчиком в виде проекта, реализованного на ПЛИС (например, типа Xilinx), и перед началом работы необходимо произвести автоматический перевод проекта в базис библиотеки БМК. Так же, при проектировании сложного цифрового устройства, заказчиком предоставляется SDC файл (Synopsys Design Constraints), который содержит различные временные параметры и ограничения, например, информацию о тактовых сигналах, задержках на входах и выходах микросхемы и др. Последним важным элементом, предоставляемым заказчиком, является файл, содержащий тестовые последовательности сигналов, с помощью которых производится верификация разрабатываемого устройства на различных этапах проектирования, а так же проверка работоспособности изготовленной микросхемы.

Ко второй группе исходных данных, необходимых для проектирования СБИС, относятся библиотеки стандартных элементов БМК. Как правило, данная информация предоставляется Изготовителем (полупроводниковой фабрикой, которая по окончании разработки микросхемы будет ее производить).

Логическое проектирование СБИС ( front-end design)

Основным этапом логического проектирования является логический синтез. В общих чертах, синтез представляет собой генерацию списка логических вентилей и их межсоединений. Для этого используются системы автоматического проектирования (САПР) от производителей Cadence (например, Encounter RTL Compiler), Synopsys, Mentor Graphics или др.

Если рассматривать процесс логического синтеза более подробно, то можно сказать что он состоит из двух этапов. На первом этапе происходит минимизация логических функций цифрового устройства [2]. В данном случае под логической функцией следует понимать функцию, которая в зависимости от данных на входе микросхемы выдает информацию с конкретного выхода микросхемы. Второй этап заключается в построении логической схемы из стандартных элементов библиотеки БМК, в соответствии с минимизированными логическими функциями.

Как уже было сказано ранее, в результате логического синтеза мы получаем список логических вентилей и их межсоединений (netlist). Далее необходимо провести логическое моделирование дизайна СБИС. Это означает, что необходимо проверить все функциональные параметры и характеристики устройства на логическом уровне, используя тестовые последовательности сигналов.

Если результаты проверки оказались неудовлетворительными, то необходимо заново провести логический синтез и/или откорректировать формальное описание проекта.

Физическое проектирование СБИС ( back-end design)

Как правило, маршрут физического проектирования состоит из следующих этапов:

1. Разбиение на модули (Partitioning)

Первоначально структура устройства разбивается на отдельные модули в соответствии с его логикой и видом дерева синхронизации.

2. Топологическое размещение (Floorplanning)

Под топологическим размещением понимают расположение на кристалле основных модулей, структуры периферийных элементов и др.

3. Размещение базовых элементов (Placement)

На данном этапе происходит размещение базовых библиотечных элементов БМК в модулях.

4. Построение дерева синхронизации (Clock Tree Synthesis)

Построение дерева синхронизации заключается в соединении всех элементов, зависящих от тактового сигнала (например, триггеров), с входом микросхемы, на который подается синхросигнал.

5. Разводка межсоединений (Routing)

При разводке (трассировке) межсоединений происходит соединение базовых библиотечных элементов и модулей между собой, в соответствии с логикой устройства.

6. Экстракция паразитных сопротивлений и емкостей межсоединений (Extraction)

Данный этап позволяет выявить и по возможности ликвидировать паразитные сопротивления и емкости, порождаемые спроектированной топологией межсоединений.

7. Проверка работоспособности спроектированной СБИС с добавленной паразитной нагрузкой на межсоединения.

На данном этапе производится финальная верификация спроектированной микросхемы перед началом производства. Если какие-либо параметры СБИС не удовлетворяют требованиям, предоставляемым к устройству, то все этапы физического проектирования повторяются до получения необходимого результата. Однако, как уже говорилось ранее, в некоторых случаях повторение этапов физического проектирования не приводят к желаемому результату. В таких условиях приходится возвращаться к этапу логического проектирования и/или корректировке формального описания проекта.

Заключение

Стоит отметить, что идеи, изложенные ранее, имеют общий характер. На практике, вид маршрута проектирования цифровой СБИС может несколько отличаться от представленного (см. рис. 1). Например, при разработке простого устройства, можно опустить разбиении на модули во время этапа физического проектирования, а при разработке микросхемы со сложной логикой и архитектурой, отдельные модули могут независимо разрабатываться как отдельные СБИС.

Список литературы:

1.Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. 2-е изд., перераб. и доп. СПб.: БХВ-Петербург, 2005. — 800 с.

2.Уэйкерли Дж.Ф.. Проектирование цифровых устройств, том 2. М: Постмаркет, 2002. — 528 с.

дипломов