Статья опубликована в рамках: XXXVII Международной научно-практической конференции «Научное сообщество студентов XXI столетия. ТЕХНИЧЕСКИЕ НАУКИ» (Россия, г. Новосибирск, 24 декабря 2015 г.)

Наука: Информационные технологии

Скачать книгу(-и): Сборник статей конференции

- Условия публикаций

- Все статьи конференции

дипломов

МОДЕЛИРОВАНИЕ ФУНКЦИОНИРОВАНИЯ ТРАКТА ДАННЫХ ПРОЦЕССОРА НА ОСНОВЕ 3D ОЗУ В СРЕДЕ LABVIEW

Горшенин Николай Олегович

студент 3 курса, кафедры «Информационных и измерительных технологий» ЮФУ,

РФ, г. Ростов-на-Дону

E-mail: titanus-maximus@yandex.ru

Рябошапко Борис Валентинови

E-mail: rbv2.7182@gmail.com

научный руководитель, канд. техн. наук, доцент кафедры «Информационных и измерительных технологий» ЮФУ,

РФ, г. Ростов-на-Дону

В настоящее время компьютеры стали неотъемлемой частью нашей жизни. Группы ученых по всему миру работают над улучшением аппаратных средств компьютера с целью уменьшить размеры и стоимость компонентов, при этом улучшив их характеристики. Современная архитектура предполагает наличие такого элемента, как оперативное запоминающее устройство (ОЗУ), представляющего собой «энергозависимую память с произвольным доступом к ячейкам» [4, с. 140] (прочитать или записать данные можно в любой момент времени в отличие от, например, магнитной ленты, представляющей собой запоминающее устройство последовательного доступа). Ячейки памяти ОЗУ объединены в огромные матрицы и в простейшем случае на базе конденстаторов, принимающих два состояния: логическую единицу, когда он разряжен, либо ноль при наличии заряда, и транзисторных ключей, которые могут или удерживать заряд на конденсаторе или открывать ячейки для считывания. Процедура чтения реализуется следующим образом (рис. 1): на нужную строку ячеек памяти, подаётся сигнал, открывающий транзисторный ключ, который в свою очередь пропускает электрический заряд, содержащийся или отсутствующий в конденсаторе, на соответствующий столбец. К каждому из столбцов подключен чувствительный усилитель заряда, реагирующий даже на незначительный поток электронов выпущенных с конденсатора.

Рисунок 1. Работа с матрицей ячеек памяти

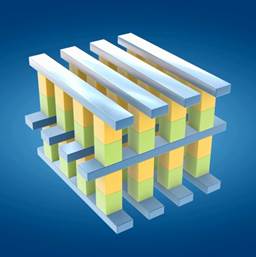

К сожалению, в данный момент используются лишь ОЗУ с одноуровневой матрицей ячеек. Однако не так давно компания Intel анонсировала совершенно новую технологию памяти, способную кардинально изменить архитектуру компьютера и получившую название 3D XPoint. Как известно, традиционные компьютеры сочетают в себе два вида памяти: высокоемкую энергозависимую память (ПЗУ) и энергозависимую оперативную память (ОП). Технология 3D Xpoint призвана объединить ОЗУ и ПЗУ в единую память, особенностями которой являются энергонезависимость, высокая скорость и повышенная плотность ячеек, что позволит значительно увеличить объемы памяти при неизменных размерах модуля. Его структура показана на рис. 2.

Рисунок 2. Структура модуля памяти 3D XPoint

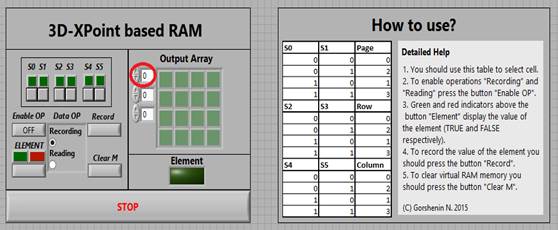

«Провода, сгруппированные ортогонально, соединяются в колонки микроскопических размеров» [3]. Вместо привычных транзисторов новый вид памяти для считывания или записи информации предполагает использование селекторов, позволяющих выбрать необходимую ячейку в зависимости от величины прикладываемого напряжения. За счет многослойной структуры, энергонезависимости и применения новых методов выбора записываемых (считываемых) ячеек развитие технологии 3D XPoint можно считать крайне важной и перспективной задачей. В рамках данной статьи представлено моделирование работы памяти по указанным выше принципам в “среде визуального программирования LabVIEW” [1, c. 19]. Уникальность проведенного исследования состоит в том, что используя такие элементы цифрового логического уровня, как мультиплексор и демультиплексор, мы смогли построить работоспособную модель ОЗУ, базирующуюся на технологии 3D XPoint. На рис. 3 представлена лицевая панель виртуального прибора.

Рисунок 3. Лицевая панель виртуального прибора

Начнем рассмотрение программы с ее функциональных возможностей. Память была представлена в виде матрицы типа boolean размером 4x4x4, выбор необходимого элемента осуществляется с помощью управляющих сигналов S0,S1..S5 в соответствии с таблицей представленной справа на рис. 3. Нажатие кнопки “Enable OP” дает разрешение на выполнение операции чтения, либо записи, которые в свою очередь выбираются при помощи группы радио-кнопок “Data OP”. В случае записи, необходимо задать значение элемента. Это возможно сделать по нажатию кнопки “Element”, над которой находятся 2 светодиодных индикатора, отображающих текущее значение записываемого элемента (по умолчанию – логический ноль, что соответствует красному светодиоду). После этого необходимо нажать кнопку “Record”, чтобы была произведена запись. При первом запуске программы происходит очистка всех переменных и матрицы памяти, но если у пользователя появилась необходимость очистить память в процессе работы – он может осуществить эту операцию путем нажатия кнопки “Clear M“. Выбор страницы матрицы памяти осуществляется изменением индекса, обведенного кругом на рис. 3. При работе важно учитывать тот факт, что нумерация строк, столбцов и страниц в программе начинается с нуля. После небольшого обзора функциональных возможностей программы перейдем к рассмотрению блок-диаграммы (рис. 4) и особенностей программирования.

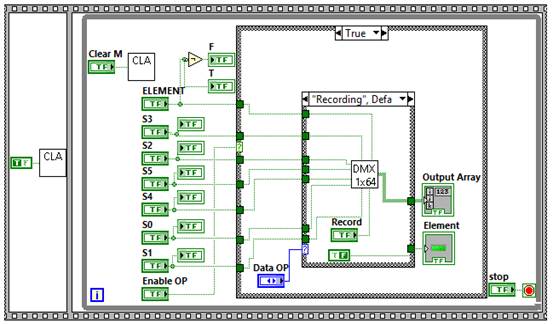

Рисунок 4. Блок-диаграмма виртуального прибора

Как видно из рис. 4, в программе используются следующие структуры: Flat Sequence (используется для того, чтобы вызвать подприбор “CLA”, позволяющий обнулить данные, перед началом работы основной программы), While Loop (служит для поддержания работы виртуального прибора, вплоть до нажатия кнопки “Stop”), «Case Structure» [2, c. 27] (применяется для реализации разрешения на выполнение и выбора соответствующей операции). Вся программа базируется на использовании подприборов, реализованных по принципу вложенности (например, для создания SubVI “DMX 1x64” предварительно разрабатывались “DMX 1x2”, “DMX 1x4”, “DMX 1x8” и так далее, группируя которые мы, в итоге, смогли реализовать названный выше 64-х канальный демультиплексор). Разберем более подробно принцип, по которому происходит запись элемента в необходимую ячейку. Для корректной реализации процессов записи и чтения мы воспользовались глобальной переменной – многомерной матрицей размера 4x4x4. При первичном запуске программы данная матрица обнуляется и передается в 64-х канальный демультиплексор, который записывает в определенную ячейку матрицы заданный элемент в соответствии с управляющими сигналами S0,S1..S5. Значения глобальной переменной передаются на матрицу “Output Array”, состоящую из светодиодных индикаторов, которые позволяют судить о значении элемента в ячейке памяти. Для реализации операции чтения используется 64-х канальный мультиплексор (SubVI “MUX 64x1”), который при поступлении комбинации управляющих сигналов выбирает соответствующую ячейку памяти и передает ее значение на светодиодный индикатор “Element”.

Результаты работы подтвердили возможность создания ОЗУ, базирующегося на технологии 3D XPoint, а также позволили рассмотреть на практике преимущества нового вида памяти. Применение среды визуального программирования LabVIEW позволило осуществить моделирование, сохранив наглядность и доступность для простого пользователя, что делает возможным использование данного виртуального прибора в образовательных целях.

Список литературы:

- Блюм П., LabVIEW: стиль программирования. Пер. с англ. под ред. Михеева П. – М.: ДМК Пресс, 2008 – 400 с.

- Виноградова Н.А., Листратов Я.И., Свиридов Е.В. Разработка прикладного программного обеспечения в среде LabVIEW: Учебное пособие – М.: Издательство МЭИ, 2005. – 50 с.

- Гордон М.У. Предмет исследования защиты информации // PCWorld – 2015 / [Электронный ресурс]. – Режим доступа: – URL: http://www.pcworld.com/article/2973549/storage/intels-crazy-fast-3d-xpoint-optane-memory-heads-for-ddr-slots-but-with-a-catch.html (дата обращения: 17.12.2015).

- Таненбаум Э. Архитектура компьютера 5-е изд. – СПб.: 2007 – 844 с.

дипломов