Статья опубликована в рамках: XLV Международной научно-практической конференции «Технические науки - от теории к практике» (Россия, г. Новосибирск, 28 апреля 2015 г.)

Наука: Технические науки

Секция: Информатика, вычислительная техника и управление

Скачать книгу(-и): Сборник статей конференции

- Условия публикаций

- Все статьи конференции

дипломов

Статья опубликована в рамках:

Выходные данные сборника:

COPACOBANA . ОСОБЕННОСТИ РАЗРАБОТКИ И РЕАЛИЗАЦИИ

Тюрин Сергей Феофентович

д-р техн. наук, профессор, Пермский национальный исследовательский политехнический университет, профессор кафедры, РФ, г. Пермь

E -mail: tyurinsergfeo@yandex.ru

Андреев Роман Александрович

студент Пермского национального исследовательского политехнического университета, РФ, г. Пермь

E -mail: abusedroman@gmail.com

Феофилова Полина Андреевна

студент Пермского национального исследовательского политехнического университета, РФ, г. Пермь

COPACOBANA. THE FEATURES OF DESIGN AND REALIZATION

Tyurin Sergey

doctor of technical sciences, professor of Perm national research polytechnic university, Russia, Perm

Andreev Roman

student of Perm national research polytechnic university, Russia, Perm

Feofilova Polina

student of Perm national research polytechnic university, Russia, Perm

АННОТАЦИЯ

В данной статье рассмотрена разработка и реализация суперкомпьютера Copacobana, который может использоваться для надежной оценки безопасности криптографических алгоритмов, таких как RSA and ECC.

ABSTRACT

This paper reviews the design and realization of the Copacobana machine, which can be used for a reliable security estimation of cryptosystems such as RSA and ECC.

Ключевые слова: ППВМ; криптоаналитическое устройство; надежность криптографических алгоритмов.

Keywords: FPGA; cryptanalytical machine; cryptographic algorithms’ reliability.

Все современные применяющиеся на практике шифры, будь то симметричные или ассиметричные, используют параметры безопасности, которые защищают их от атак с компьютеров. В зависимости от маржи безопасности, выбранной в данном приложении, многие шифры потенциально уязвимы для атак спецтехники, которая имеет соотношение цена-качество на несколько порядков лучше, чем в современных компьютерах. В данной статье описывается конструкция и успешная реализация прототипа криптоаналитического устройства специального назначения на базе недорогих ППВМ (программируемая пользователем вентильная матрица).

Copacobana — массово-параллельное устройство, основанное на ППВМ. Оборудование подходит для вычислительных задач, которые являются параллелизуемыми и имеют низкие требования к связи и может использоваться, например, для атаки на криптосистемы на основе эллиптических кривых. Даже, несмотря на то, что нарушение алгоритмов RSA (1024 бит или больше) или ECC (160 бит или больше) находится вне досягаемости Copacobana, оно предусматривает возможность для надежной оценки безопасности RSA и ECC. Еще более актуальным является тот факт, что ограниченные ресурсы приложений, в частности мобильных устройств, иногда определяются короткими параметрами, такими как 112-битные и 128-битные систем ECC, рекомендованные стандартом SECG, которые становятся уязвимыми в устройстве. Кроме того, по закону Мура, можно предсказать надежность RSA и ECC в ближайшие годы. Текущие реализации базового контроля доступа применяют симметричную криптографию (Triple DES) и генерируют соответствующие ключи шифрования и аутентификации из паспортных данных.

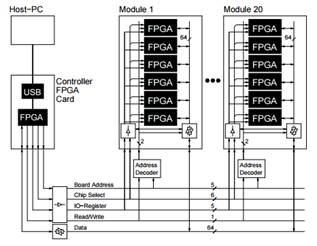

Оптимизированный по стоимости параллельный дешифровщик (Copacobana) состоит из множества независимых недорогих ППВМ, подключенных к центральному компьютеру через стандартный интерфейс, например, USB или Ethernet. Кроме того, такой стандартный интерфейс позволяет легко расширить центральный компьютер более чем одним устройством Copacobana. Запуск ППВМ, контроль и накопление результатов производится центральным компьютером. Поскольку криптоаналитические приложения требуют большое количество вычислительной мощности, специальная платформа объединяет вплоть до 120 ППВМ (Spartan3-1000). Построение системы такого размера с коммерчески доступными платами ППВМ, конечно, возможно, но очень дорого. Поэтому разработчики Copacobana решили спроектировать и создать собственно оборудование. Реализация оптимизированного по стоимости проекта стала возможной только путем строго ограничения всех функциональных возможностей до непосредственно необходимых для взлома кодов, чтобы сделать несколько вариантов на основе легкодоступных компонентов и интерфейсов. Констукция Copacobana изображена на рисунке 1 и состоит из:

· ППВМ модулей для фактической реализации представленных аппаратных архитектур,

· системной платы, соединяющей все модули ППВМ с общей шиной данных, шиной адреса и питания,

· платы контроллера, подключающей шину данных и адресную шину к хост-компьютеру через USB.

Рисунок 1. Архитектура Copacobana

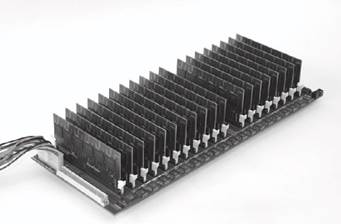

Модули ППВМ: Было решено использовать недорогие, современные ППВМ для проектирования: Xilinx Spartan3-1000. Данная ППВМ имеет 1 миллион системных портов, 17280 эквивалентных логических ячеек, 1920 конфигурируемых логических блоков, эквивалентных 7680 секторам, 120 килобит динамической оперативной памяти, 432 килобита блочной оперативной памяти и 4 цифровых блока управления синхронизацией. Выбор данной ППВМ был сделан путем сравнения размеров и цены различных типов и серий ППВМ. Разработчики решили остановиться на небольших модулях в стандартном формате двустороннего модуля памяти, включающих в себя 6 ППВМ Xilinx XC3S1000. Рисунок 2 показывает эту реализацию на примере сделанной вручную четырехслойной печатной платы. ППВМ непосредственно соединены с общей 64-битной шиной данных на плате модуля ППВМ, который сопряжен с шиной данных соединительной платы через приемопередатчики с тремя состояниями выхода. В то время как ППВМ отключены от шины, они могут взаимодействовать локально через внутреннюю 64-битную шину на двустороннем модуле памяти. Данный формат двустороннего модуля памяти позволяет осуществить компактное расположение компонентов, что очень важно для тесно связанных шиной модулей.

Рисунок 2. Модуль ППВМ

Соединительная плата: соединительная плата связывает все модули ППВМ и плату контроллера. Все модули соединены 64-битной шиной данных и 16-битной адресной шиной. Одну такую мастер-шину легко контролировать, так как не требуется система разрешения конфликтов. Обработка прерываний полностью избегается для того чтобы сохранить максимально простую конструкцию. Если распределение передачи данных заранее неизвестно, мастер-шине нужно будет опрашивать ППВМ. Кроме того, питание подается на каждый модуль ППВМ и интерфейс контроллера. Соединительная плата распределяет два тактовых сигнала от платы контроллера к слотам. Каждому модулю ППВМ присваивается уникальный аппаратный адрес, который создается с помощью типовой матричной логики, подключенной к каждому разъему DIMM. Таким образом, все ядра ППВМ могут иметь одинаковую конфигурацию и все модули ППВМ могут иметь одинаковую топологию. Они могут быть легко заменены в случае дефекта. На рисунке 3 показан прототип соединительной платы, оснащенной одним модулем ППВМ и платой интерфейса системы управления, которая будет описана далее.

Рисунок 3. Соединительная плата

Интерфейс управления: Передача данных от и до ППВМ и к хост-компьютеру осуществляется интерфейсом управления. Была выбрана небольшая макетная плата с ППВМ (CESYS USB2FPGA). Макетная плата включает в себя Xilinx XC2S200 Spartan II FPGA (PQ208), встроенный контроллер USB (CYPRESS FX-2) и 1 Мбайт статической памяти с произвольным доступом (SRAM). Кроме того, плата имеет 96-контактный разъем для подключения к ней. В более поздних версиях конструкции можно заменить макетную плату ППВМ микроконтроллером со стандартным USB или интерфейсом Ethernet. Аппаратный контроллер должен обеспечивать согласование различных тактовых частот: интерфейс USB использует тактовую частоту 24 МГц, базовая плата — 33 МГц, а сам контроллер работает на внутренней тактовой частоте 133 МГц. Главные задачи интерфейса управления заключаются в том, что он используется для декодирования и выполнения команд хоста, полученных с помощью USB, для программирования ППВМ через шину данных в параллельном подчиненном режиме, для инициализации ППВМ и старта вычислений, и регулярного опроса ППВМ для получения результатов.

Хост-компьютер: объектом верхнего уровня Copacobana является хост-компьютер, который используется для программирования и управления всеми работающими ППВМ. Для этого была написана библиотека программ, чтобы давать команды плате контроллера Copacobana, которая подключена через USB. Все программы системного программного обеспечения основаны на библиотеке с закрытым исходным кодом, предоставленной производителем платы (CESYS). Дополнительные функции включают в себя обнаружение аппаратных средств и некоторые процедуры настройки, такие как перезапуск соединительной платы. Функции более высокого уровня включают в себя команды на прикладном уровне. Например, для DES Cracker, можно хранить определенный исходный текст в единицах DES, проверять его статус, и т. д.

В данной работе был описан проект экономически-эффективного устройства Copacobana, которое может быть реализовано менее чем за 10000 долларов и содержать 120 недорогих ППВМ. Оно было предназначено для решения проблем шифрования, но не ограничивается этим. Будут существовать более интересные проблемы, которые могут быть эффективно решены с помощью этого устройства.

Список литературы:

1.Sandeep Kumar, Christof Paar, Jan Pelzl , Gerd Pfeiffer, Manfred Schimmler «Breaking ciphers with COPACOBANA — a cost-optimized parallel code breaker», Chair for Embedded Security Ruhr-University Bochum, Germany; Electrical Department of the University of Kiel, Germany, 2006.

дипломов